-

[SystemVerilog] 랜덤변수 3개발/SystemVerilog 2022. 1. 27. 01:09

제약조건이 너무 복잡한 경우가 있다.

이럴땐 함수를 정의하여 제약조건을 적용할 수 있다.

class packet; rand bit [3:0] start_addr; rand bit [3:0] end_addr; constraint start_addr_c {start_addr == s_addr(end_addr);}; function bit [3:0] s_addr (bit [3:0] e_addr); if (e_addr < 4) s_addr = 0; else s_addr = e_addr - 4; endfunction endclass module tb; initial begin packet pkt = new(); repeat (10) begin pkt.randomize(); $display("start = %d, end = %d", pkt.start_addr, pkt.end_addr); end end endmodule

constraint 조건을 위해서 s_addr 함수를 정의하였다.

end_addr 값에 따라서 start_addr 값이 조건에 맞게 결정된다.

변수들끼리 서로 다른값을 갖게 만들고 싶으면 unique 키워드를 넣으면 된다.

class myclass; rand bit [2:0] var1, var2, var3, var4; rand bit [2:0] arr[8]; constraint c1 {unique {var1, var2, var3, var4};}; constraint c2 {unique {arr};}; endclass module tb; myclass class1 = new(); initial begin class1.randomize(); $display("%d, %d, %d, %d", class1.var1, class1.var2, class1.var3, class1.var4,); $display("%p", class1.arr); end endmodule

위 예제에서 var1 ~ var4 는 서로 다른값이 부여된다.

배열 arr 은 원소들끼리 다른 값으로 된다. 만약 arr 크기가 9 이상이라면 적어도 두개의 원소가 서로 중복값을 갖게 되므로 오류가 발생한다. 따라서 unique 사용할 때 이 부분을 주의해야한다.

이전 글에서 가중치를 부여하기 위해서 dist 구문과 := , :/ 연산자를 설명했다.

randcase 구문도 비슷한 역할을 한다. 사용법은 case 문장과 거의 똑같다. 다만 case item은 숫자나 변수를 적는데 그 값이 가중치가 된다.

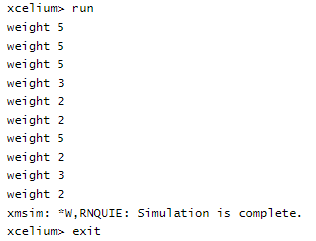

module tb; initial begin repeat (10) begin randcase 0 : $display("weight 0"); 2 : $display("weight 2"); 5 : $display("weight 5"); 3 : $display("weight 3"); endcase end end endmodule

만약 caseitem 중에서 값이 0이 있다면, 그 문장은 실행되지 않는다.

'개발 > SystemVerilog' 카테고리의 다른 글

[SystemVerilog] 랜덤변수 2 (0) 2022.01.26 [SystemVerilog] 랜덤변수 1 (0) 2022.01.25 [SystemVerilog] 클래스 4 데이터 은닉 (0) 2022.01.24 [SystemVerilog] 클래스 3 다형성2 (0) 2022.01.24 [SystemVerilog] 클래스 3 다형성 (0) 2022.01.24