-

[SystemVerilog] 클래스 3 다형성개발/SystemVerilog 2022. 1. 24. 13:07

객체지향에서 다형성이란

베이스클래스에서 하위 클래스의 속성과 메서드를 직접 사용 할 수 있는것을 의미한다.

아래와 같은 클래스가 정의되어있다.

class packet; bit [31:0] addr; function new (bit [31:0] addr); this.addr = addr; endfunction task display(); $display("[base] addr = 0x%0h", addr); endtask endclass class extpacket extends packet; bit [31:0] data; function new (bit [31:0] addr, data); super.new(addr); this.data = data; endfunction task display(); $display("[child] addr = 0x%0h, data = 0x%0h", addr, data); endtask endclassmodule tb; packet bc; extpacket sc; initial begin sc = new(32'hfeeed_feed, 32'h1234_5678); bc = sc; bc.display(); sc.display(); end endmodule

sc 핸들을 bc에 넘겨주고 각각 메서드를 실행했다.

똑같은 display() 메서드라도 핸들이 가르키는 오브젝트가 아닌, 핸들 타입에 의해서 메서드가 결정된다.

부모클래스 핸들이 자식클래스 오브젝트를 가르키더라고 부모클래스 핸들로 자식클래스의 변수를 직접 접근할 수 없다.

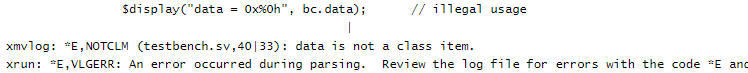

module tb; packet bc; extpacket sc; initial begin sc = new(32'hfeeed_feed, 32'h1234_5678); bc = sc; $display("data = 0x%0h", bc.data); // illegal usage end endmodule

실행하면 에러가 발생한다.

부모클래스 핸들을 자식클래스 핸들로 할당하는것도 에러가 발생한다.

module tb; packet bc; extpacket sc; initial begin bc = new(32'hfeeed_feed); sc = bc; end endmodule

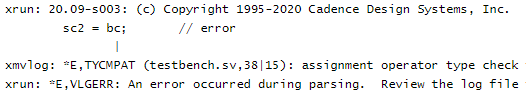

부모클래스 핸들이 이미 자식클래스를 가르키더라도 부모클래스 핸들을 다시 자식클래스 핸들로 할당하는것은 안된다.

module tb; packet bc; extpacket sc1, sc2; initial begin sc1 = new(32'hfeed_feed, 32'hface_cafe); bc = sc1; sc2 = bc; // error end endmodule

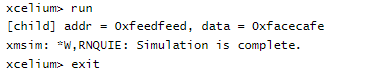

위의 오류를 해결하려면 다이나믹 캐스팅을 써야한다.

module tb; packet bc; extpacket sc1, sc2; initial begin sc1 = new(32'hfeed_feed, 32'hface_cafe); bc = sc1; $cast(sc2, bc); // dynamic cast sc2.display(); end endmodule

'개발 > SystemVerilog' 카테고리의 다른 글

[SystemVerilog] 클래스 4 데이터 은닉 (0) 2022.01.24 [SystemVerilog] 클래스 3 다형성2 (0) 2022.01.24 [SystemVerilog] 클래스 3 상속 (0) 2022.01.24 [SystemVerilog] 클래스 1 (0) 2022.01.17 [SystemVerilog] 데이터 타입 5 string (0) 2022.01.17