-

AMBA3 APB protocol 1개발/Protocol 2022. 2. 3. 22:53

AMBA™ 3 APB Protocol v1.0 Specification 기준으로 정리함

APB 프로토콜은 ARM에서 발표한 AMBA3 프로토콜 스펙 중 하나다.

APB는 높은 성능이 필요하지 않은 주변장치를 연결하는데 쓰인다. 저성능, 저전력의 프로토콜이다.

모든 신호는 clock 상승엣지에서 동작하며 하나의 트랜잭션에 적어도 2사이클이 소모된다.

아래에 APB의 신호들이 정리되어있다.

AMBA™ 3 APB Protocol v1.0 Specification, Table 4-1 APB signal descriptions APB의 모든 신호들은 P로 시작한다.

PCLK은 APB master / slave 에 적용되는 공통 클락이다. 다른 신호들은 PCLK 상승엣지에 맞춰서 동작한다.

PRESETn 은 APB master / slave asynchronous 리셋신호다.

PADDR 는 slave의 주소를 나타낸다.

PSELx 는 APB master가 슬레이브를 선택할때 쓰는 신호다. 슬레이브의 갯수만큼 PSEL 신호가 있고 트랜잭션 한번에 하나의 PSEL 신호만이 set 된다.

PENABLE 는 slave가 쓰기 / 읽기 동작을 수행하도록 지시한는 신호다. PREADY와 함께 handshake 신호이다.

PWDATA / PRDATA 각각 쓰기 읽기 데이터 신호다.

PWRITE 는 트랜잭션이 읽기 / 쓰기 인지 구분하는 신호다. 1이면 쓰기, 0이면 읽기다.

PSLVERR 는 트랜잭션이 fail 발생했을때 slave에서 보내는 신호다. 필수적인 신호는 아니다.

해당 신호가 필요없다면 0으로 고정해야한다.

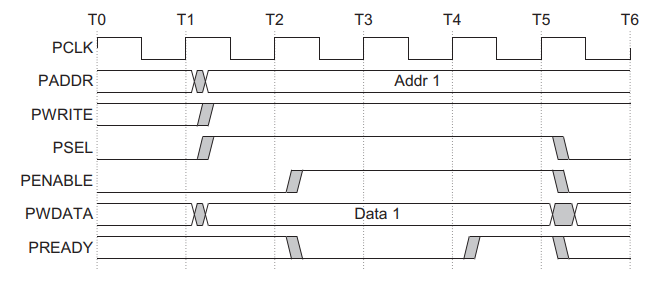

APB 프로토콜을 이용해 쓰기를 할 때의 신호를 알아본다.

APB write 는 wait state / no wait state 두가지가 있다.

먼저 no wait state 는 2 사이클만에 쓰기를 완료한다.

no wait state 쓰기를 하기 위해선 PWRITE가 1이 되고, PADDR / PWDATA에 값을 넣는다.

그리고 쓰려고 하는 slave를 선택하는 PSEL 신호를 set 한다.

T1 ~ T2가 첫번째 사이클이고, 이를 setup phase라고 한다.

그 후 PENABLE / PREADY 신호가 동시에 들어와 T3때 handshake하여 슬레이브에 PWDATA 값이 전송된다.

이것이 두번째 사이클이며, T2 ~ T3를 access phase 라고 한다.

2사이클 만에 트랜잭션이 완료된 경우다.

트랜잭션이 완료되면 PENABLE / PREADY / PSEL 신호들은 low가 된다.

그리고 PADDR / PWRITE 신호는 그 값을 유지한다. 이는 신호 스위칭을 줄여서 전력소모를 줄이기 위함이다.

wait state는 이보다 사이클이 더 길다.

이는 PREADY신호가 늦게 set 되기 때문이다.

PADDR / PWDATA / PSEL / PWRITE 신호가 setup phase에서 set 된 후 다음 사이클에서 PENABLE이 set 된다.

하지만 PREADY가 늦게 set 되어서 T5에 트랜잭션이 완료된다. T2 ~ T5 가 access phase 이다.

PREADY가 set 될 때 까지 다른 신호들은 계속 유지되야한다.

트랜잭션이 끝나고 PENABLE이 0으로 되면 PREADY 값은 0 / 1 아무 값이 될 수 있다.

PREADY 값이 1으로 유지되면 다음 트랜잭션은 2사이클 만에 완료될 것이다.

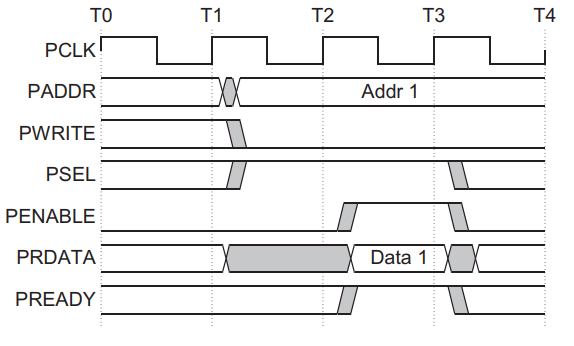

쓰기를 알아봤으니 읽기를 할 때 신호를 알아본다.

읽기도 마찬가지로 PREADY가 set 되는 시점에 따라서 wait state / no wait state 으로 구분된다.

읽기를 할 땐 setup phase 에서 PADDR, PSEL 신호를 set하고 PWRITE 신호를 0으로 한다.

그 후 access phase 에서 PENABLE / PREADY 신호가 handshake 하여 PRDATA 값을 master로 보낸다.

slave는 읽기 트랜잭션이 끝나기 전에 PRDATA를 제공해야 한다.

PREADY가 늦게 뜨면 3사이클 이상이 소모된다.

이때 PREADY가 1이 될 때 까지 다른 신호들은 유지되어야 한다.

'개발 > Protocol' 카테고리의 다른 글

AMBA3 APB protocol 2 (0) 2022.02.03